## 100V Half-Bridge SolidGaN with Integrated Gate Driver

### 1. Features

- · 2.4mΩ Half-Bridge GaN FETs with Gate Driver

- · 80V Continuous, 100V Transient Voltage Rating

- · Capable of up to 5MHz Switching

- · Independent High-Side and Low-Side PWM Inputs

- Internal Strong and Smart Bootstrap Switch

- · Fast Propagation Delay (14ns Typical)

- Excellent Delay Matching (1ns Typical)

- · Built-In UVLO, OVLO, OTP Protections

- · 35µA Low VCC Quiescent Current

- Integrated VCC/BST capacitors

- · High dv/dt Immunity up to 50V/ns

- Adjustable Turn-on Speeds

- · Optimized for Easy and Low-EMI PCB Layout

- · LGA 5mmx6.5mm Package, 1.12mm Profile

### 2. Applications

- · Half Bridge, Full Bridge, SR in LLC Converters

- High Frequency Buck and Boost Converter

- Datacenter and Automotive Power Supply

- · Class-D Audio, Motor Drive Applications

### 3. Description

The ISG3202 is a 100V, 60A, half-bridge SolidGaN in a compact 5mm x 6.5mm LGA package. Included in the package are two high-performance enhancement-mode GaN FETs, drivers, gate resistors, and driver supply capacitors, offering the industry's most compact and efficient GaN power solution.

The ISG3202 provides two logic inputs for controlling the high-side and low-side GaN FETs for maximum flexibility. The split driver outputs allow for independent adjustment of turn-on and turn-off strengths, optimizing both EMI and efficiency.

Comprehensive fault protection is built into the ISG3202, including active bootstrap (BST) voltage control to prevent overcharge and ensure stable gate drive voltage, independent undervoltage and overvoltage protection for both VCC and BST, and over temperature protection.

With fast propagation delay, excellent delay matching, superior dv/dt immunity, and ultra-low in-package parasitic inductance loop, the ISG3202 enables designers to achieve substantial improvement in power density and efficiency.

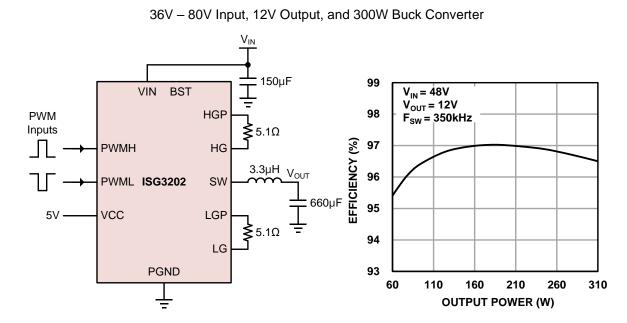

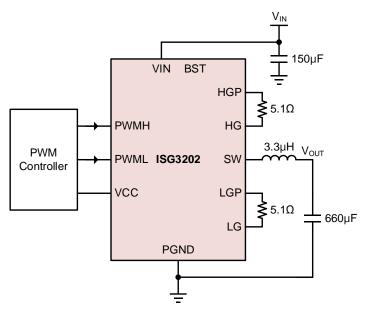

## 4. Typical Application

### **POWER THE FUTURE**

## **Table of Contents**

| 1.  | Features                         |    |

|-----|----------------------------------|----|

| 2.  | Applications                     | 1  |

| 3.  | Description                      | 1  |

| 4.  | Typical Application              | 1  |

| 5.  | Revision History                 | 2  |

| 6.  | Pin Configuration and Functions  | 3  |

| 7.  | Absolute Maximum Ratings         | 4  |

| 8.  | ESD Ratings                      | 4  |

| 9.  | Recommended Operating Conditions | 4  |

| 10. | Thermal Information              | 4  |

| 11. | Electrical Characteristics       | 5  |

| 12. | Switching Characteristics        | 6  |

| 13. | Typical Characteristics          | 7  |

| 14. | Block Diagram                    | 11 |

| 15. | Function Description             | 12 |

| 16. | Package Information              | 20 |

| 17. | Tape and Reel Information        | 21 |

| 18. | Recommended Land Pattern         | 23 |

| 19. | Order Information                | 23 |

|     |                                  |    |

## 5. Revision History

#### Major changes since the last revision

| Revision | Date       | Description of changes    |

|----------|------------|---------------------------|

| 1.0      | 2024-05-20 | Final datasheet release   |

| 1.1      | 2024-07-26 | Update thermal resistance |

Page 2

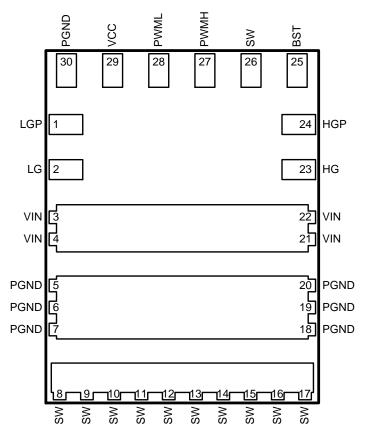

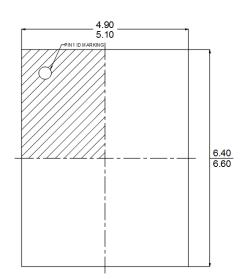

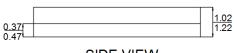

## 6. Pin Configuration and Functions

30-Lead LGA (5mm x 6.5mm) Package - Top View

| Pin Number    | Pin Name | Description                                                                            |  |  |  |  |  |

|---------------|----------|----------------------------------------------------------------------------------------|--|--|--|--|--|

| 1             | LGP      | Low-Side Gate Driver Source-Current Output. An optional resistor between LGP and       |  |  |  |  |  |

| I             | LGP      | LG can be employed to adjust turn-on speed of low side GaN FET.                        |  |  |  |  |  |

| 2             | LG       | Low-Side Gate Terminal.                                                                |  |  |  |  |  |

| 3-4,21-22     | VIN      | Input Voltage Supply. Locally bypass this pin to PGND with ceramic capacitors          |  |  |  |  |  |

| 5-7,18-20, 30 | PGND     | Power Ground.                                                                          |  |  |  |  |  |

| 8-17          | SW       | Switching Node for Main Power.                                                         |  |  |  |  |  |

| 23            | HG       | High-Side Gate Terminal.                                                               |  |  |  |  |  |

| 24            | HGP      | High-Side Gate Driver Source-Current Output. An optional resistor between HGP and      |  |  |  |  |  |

| 24            |          | HG can be employed to adjust turn-on speed of high side GaN FET.                       |  |  |  |  |  |

| 25            | BST      | High-Side Gate Driver Bootstrap Rail. Two 0.1uF ceramic capacitors are integrated      |  |  |  |  |  |

| 25            |          | between BST and SW pins, and external bootstrap capacitor is optional.                 |  |  |  |  |  |

| 26            | 26 SW    | Switching Node for Gate Drive Loop. SW waveform can be monitored. Pin 26 is            |  |  |  |  |  |

| 20            |          | connected to Pin 8-17 internally and no external connection is necessary.              |  |  |  |  |  |

| 27            | PWMH     | High-Side Driver PWM Input. This pin has an internal 200k $\Omega$ pull-down resistor. |  |  |  |  |  |

| 28 PWML       |          | Low-Side Driver PWM Input. This pin has an internal 200k $\Omega$ pull-down resistor.  |  |  |  |  |  |

| 20            | VCC      | External 5V Driver Supply. Two 0.1uF ceramic capacitors are integrated between VCC     |  |  |  |  |  |

| 29            | VUU      | and PGND pins, and external decoupling capacitor is optional.                          |  |  |  |  |  |

#### Page 3

#### **POWER THE FUTURE**

### 7. Absolute Maximum Ratings

All pins are referred to PGND pins, unless otherwise specified. Stress beyond the absolute maximum ratings can cause permanent damage or deteriorate device reliability and lifetime.

| Parameter                                                               | Min     | Max                   | Unit |

|-------------------------------------------------------------------------|---------|-----------------------|------|

| Drain-to-Source Voltage of Internal GaN FET                             |         | 100                   | V    |

| VIN                                                                     |         | 100                   | V    |

| VCC, BST to SW                                                          | -0.3    | 6.0                   | V    |

| SW                                                                      | -5      | 100                   | V    |

| BST                                                                     | -0.3    | 105                   | V    |

| HGP, HG                                                                 | Vsw-0.3 | V <sub>BST</sub> +0.3 | V    |

| LGP, LG                                                                 | -0.3    | 6.0                   | V    |

| PWMH, PWML                                                              | -0.3    | 6.0                   | V    |

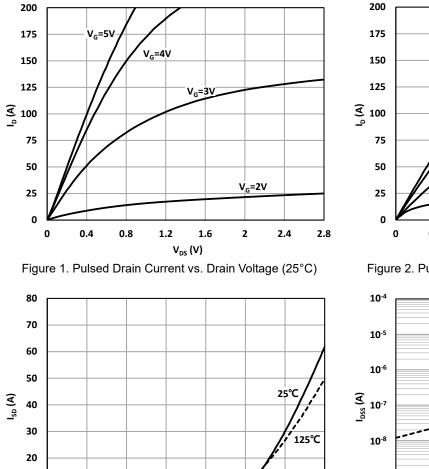

| Continuous Current for Internal GaN FET                                 |         | 60 (1)                | А    |

| Pulsed Current for Internal GaN FET (25°C, T <sub>Pulse</sub> = 100 µs) |         | 230                   | А    |

| Operating Junction Temperature TJ                                       | -40     | 150                   | °C   |

| Storage Temperature                                                     | -40     | 150                   | °C   |

(1) Ideal thermal condition. In real application the current capability depends on system thermal design.

### 8. ESD Ratings

| Parameter                                        | Value | Unit |

|--------------------------------------------------|-------|------|

| Human Body Model (HBM), per JESD22-A114 (2)      | ±1500 | V    |

| Charged Device Model (CDM), per JESD22-C101F (3) | ±1000 | V    |

(2) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(3) JEDEC document JEP155 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 9. Recommended Operating Conditions

| Parameter                                     | Min    | Max    | Unit |

|-----------------------------------------------|--------|--------|------|

| VIN                                           | 0      | 80     | V    |

| VCC                                           | 4.5    | 5.5    | V    |

| PWMH, PWML                                    | 0      | 5.5    | V    |

| SW                                            | -4     | 80     | V    |

| BST                                           | SW+4.5 | SW+5.5 | V    |

| SW Slew Rate                                  |        | 50     | V/ns |

| Operating Junction Temperature T <sub>J</sub> | -40    | 125    | °C   |

### **10. Thermal Information**

| Symbol            | Parameter                                   | Value | Unit |

|-------------------|---------------------------------------------|-------|------|

| R <sub>θJA</sub>  | Thermal Resistance, Junction to Ambient     | 59    | °C/W |

| Rejc(top)         | Thermal Resistance, Junction to Case Top    | 14.8  | °C/W |

| Rejc(bot)         | Thermal Resistance, Junction to Case Bottom | 4.1   | °C/W |

| T <sub>sold</sub> | Reflow soldering temperature                | ≤260  | °C   |

\*According to standards defined in JESD51 and JESD51-1, thermal characteristic of the package is simulated. R<sub>0JA</sub> is

Page 4

#### **POWER THE FUTURE** -

determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board.

### **11. Electrical Characteristics**

| Parameter                                 | Symbol                 | Min | Тур  | Max | Unit | Test Condition                            |

|-------------------------------------------|------------------------|-----|------|-----|------|-------------------------------------------|

| Supply Input                              |                        |     |      |     |      |                                           |

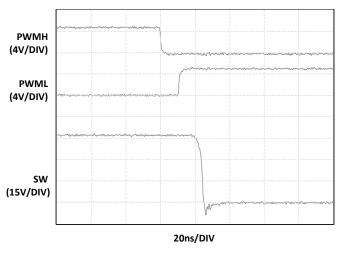

| VCC Quiescent Current                     | lcc-q                  |     | 35   | 60  | μA   | PWMH = PWML = 0                           |

| VCC Operating Current                     | ICC-OP                 |     | 20   | 30  | mA   | f = 1MHz                                  |

| BST Quiescent Current                     | IBST-Q                 |     | 40   | 70  | μA   | PWMH = PWML = 0                           |

| BST Operating Current                     | IBST-OP                |     | 20   | 30  | mA   | f = 1MHz                                  |

| VCC Overvoltage Rising                    | Vcc-ovr                | 5.7 | 6    | 6.3 | V    |                                           |

| Threshold                                 |                        |     |      |     |      |                                           |

| VCC Overvoltage Hysteresis                | V <sub>CC-OVHYS</sub>  |     | 0.25 |     | V    |                                           |

| VCC Undervoltage Rising                   | V <sub>CC-UVR</sub>    | 3.9 | 4.1  | 4.3 | V    |                                           |

| Threshold                                 |                        |     |      |     |      |                                           |

| VCC Undervoltage Hysteresis               | V <sub>CC-UVHYS</sub>  |     | 0.3  |     | V    |                                           |

| BST Undervoltage Rising                   | V <sub>BST-UVR</sub>   |     | 3.6  |     | V    |                                           |

| Threshold                                 |                        |     |      |     |      |                                           |

| BST Undervoltage Hysteresis               | V <sub>BST-UVHYS</sub> |     | 0.5  |     | V    |                                           |

| PWM Input                                 |                        |     |      |     |      |                                           |

| Input High Threshold                      | VIH                    |     | 1.8  | 2.2 | V    |                                           |

| Input Low Threshold                       | VIL                    | 0.8 | 1.2  |     | V    |                                           |

| Input Hysteresis                          | V <sub>I-HYS</sub>     |     | 0.6  |     | V    |                                           |

| Input Pull-Down Resistance                | Rı                     |     | 200  |     | kΩ   |                                           |

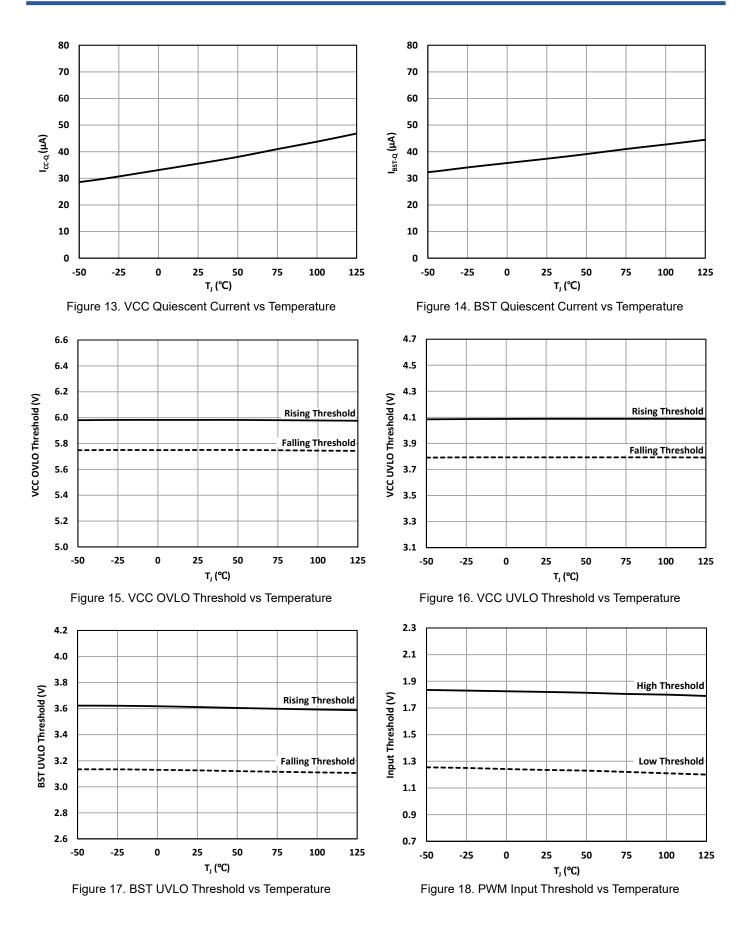

| Bootstrap Switch                          |                        |     |      |     |      |                                           |

| Switch On Resistance                      | R <sub>BST(ON)</sub>   |     | 4    |     | Ω    |                                           |

| High and Low-Side Gate Drive              | er                     |     |      |     |      |                                           |

| Output Pull-Down Resistance               | R <sub>DN</sub>        |     | 0.2  | 1   | Ω    | I <sub>HG</sub> or I <sub>LG</sub> = 10mA |

| Output Pull-Up Resistance                 | RUP                    |     | 1    | 2   | Ω    | IHGP or ILGP = -10mA                      |

| Output Peak Source Current <sup>(4)</sup> | Іон                    |     | 1.7  |     | А    | HGP = SW or LGP = PGND                    |

| Output Peak Sink Current <sup>(4)</sup>   | Iol                    |     | 4.3  |     | А    | HG = BST or LG = VCC                      |

| <b>Over Temperature Protection</b>        |                        |     |      |     |      |                                           |

| OTP Shutdown Rising                       | TOTP                   |     | 165  |     | °C   |                                           |

| Threshold <sup>(4)</sup>                  |                        |     |      |     |      |                                           |

| OTP Shutdown Hysteresis <sup>(4)</sup>    | T <sub>OTP-HYS</sub>   |     | 20   |     | °C   |                                           |

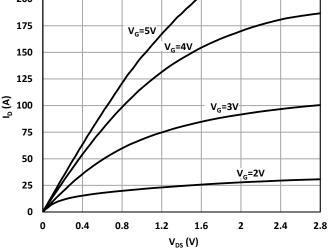

| GaN FETs                                  |                        |     |      |     |      |                                           |

| Drain-to-Source Voltage                   | BV <sub>DSS</sub>      | 100 |      |     | V    | PWML = 0V or PWMH = 0V,                   |

|                                           |                        |     |      |     |      | I <sub>D</sub> =400µA                     |

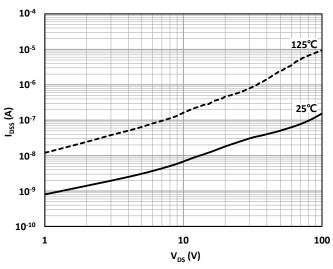

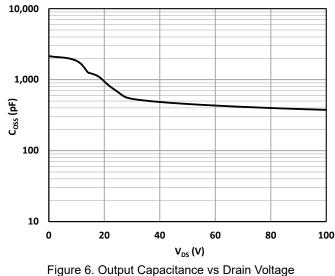

| Drain-Source Leakage                      | IDSS                   |     | 4    | 28  | μA   | PWML = 0V or PWMH = 0V,                   |

|                                           |                        |     |      |     |      | V <sub>DS</sub> = 80V                     |

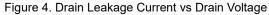

| Drain-Source On Resistance                | R <sub>DS(ON)</sub>    |     | 2.4  | 3.2 | mΩ   | PWML = 5V or PWMH = 5V,                   |

|                                           |                        |     |      |     |      | I <sub>D</sub> = 25A                      |

| Source-Drain Forward Voltage              | Vsd                    |     | 1.5  |     | V    | PWML = 0V or PWMH = 0V,                   |

Page 5

### POWER THE FUTURE •

| Parameter                          | Symbol   | Min | Тур  | Max | Unit | Test Condition              |

|------------------------------------|----------|-----|------|-----|------|-----------------------------|

|                                    |          |     |      |     |      | I <sub>S</sub> = 0.5A       |

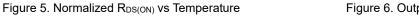

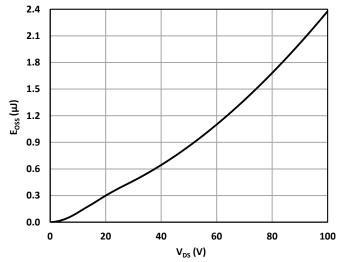

| Output Capacitance <sup>(4)</sup>  | Coss     |     | 460  |     | pF   | PWML = 0V or PWMH = 0V,     |

|                                    |          |     |      |     |      | V <sub>DS</sub> = 50V       |

| Reverse Transfer                   | Crss     |     | 8.2  |     |      | PWML = 0V or PWMH = 0V,     |

| Capacitance <sup>(4)</sup>         |          |     |      |     |      | V <sub>DS</sub> = 50V       |

| Energy Related Coss <sup>(4)</sup> | Coss(ER) |     | 700  |     |      | PWML = 0V or PWMH = 0V,     |

|                                    |          |     |      |     |      | V <sub>DS</sub> = 0V to 50V |

| Time Related Coss <sup>(4)</sup>   | Coss(TR) |     | 1020 |     |      | PWML = 0V or PWMH = 0V,     |

|                                    |          |     |      |     |      | V <sub>DS</sub> = 0V to 50V |

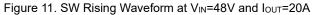

| Output Charge <sup>(4)</sup>       | Qoss     |     | 50   |     | nC   | PWML = 0V or PWMH = 0V,     |

|                                    |          |     |      |     |      | $V_{DS}$ = 0V to 50V        |

### **12. Switching Characteristics**

$T_J = 25^{\circ}C$ , VCC = BST = 5V, SW = PGND = 0V, unless otherwise noted.

| Parameter                                | Symbol            | Min | Тур | Мах | Unit | Test Condition             |

|------------------------------------------|-------------------|-----|-----|-----|------|----------------------------|

| Minimum Input Pulse Width                | TIPW              |     | 5   |     | ns   |                            |

| that Changes the Output <sup>(4)</sup>   |                   |     |     |     |      |                            |

| Minimum Gate Output Pulse                | TOPW              |     | 12  |     | ns   |                            |

| Width <sup>(4)</sup>                     |                   |     |     |     |      |                            |

| HGP Rise Time (0.5V-4.5V) <sup>(4)</sup> | T <sub>R_SW</sub> |     | 10  |     | ns   |                            |

| HG Fall Time (4.5V-0.5V) <sup>(4)</sup>  | T <sub>F_SW</sub> |     | 3   |     | ns   |                            |

| LGP Rise Time (0.5V-4.5V) <sup>(4)</sup> | T <sub>R_LS</sub> |     | 10  |     | ns   |                            |

| LG Fall Time (4.5V-0.5V) <sup>(4)</sup>  | T <sub>F_LS</sub> |     | 3   |     | ns   |                            |

| HG Turn-Off Propagation                  | T <sub>HPHL</sub> |     | 14  |     | ns   | PWMH falling to HG falling |

| Delay <sup>(4)</sup>                     |                   |     |     |     |      |                            |

| HGP Turn-On Propagation                  | THPLH             |     | 14  |     | ns   | PWMH rising to HGP rising  |

| Delay <sup>(4)</sup>                     |                   |     |     |     |      |                            |

| LG Turn-Off Propagation                  | TLPHL             |     | 14  |     | ns   | PWML falling to LG falling |

| Delay <sup>(4)</sup>                     |                   |     |     |     |      |                            |

| LGP Turn-On Propagation                  | Tlplh             |     | 14  |     | ns   | PWML rising to LGP rising  |

| Delay <sup>(4)</sup>                     |                   |     |     |     |      |                            |

| Delay Matching                           | T <sub>MON</sub>  |     | 1   |     | ns   |                            |

| LGP On and HG Off <sup>(4)</sup>         |                   |     |     |     |      |                            |

| Delay Matching                           | T <sub>MOFF</sub> |     | 1   |     | ns   |                            |

| LG Off and HGP On <sup>(4)</sup>         |                   |     |     |     |      |                            |

(4) Not 100% tested and guaranteed by design.

10

0

2.4

2.1 1.8

1.5

1.2 0.9

0.6 0.3

0.0 └ -50

Normalized Rds(on)

0

0.3

-25

0

25

50

т, (°С)

75

100

0.6

0.9

Figure 3. Source-Drain Reverse Conduction Voltage

1.2

$V_{SD}$  (V)

1.5

1.8

# Innoscience

### **13. Typical Characteristics**

Figure 2. Pulsed Drain Current vs. Drain Voltage (125°C)

Page 7

125

2.1

#### **POWER THE FUTURE**

# Innoscience

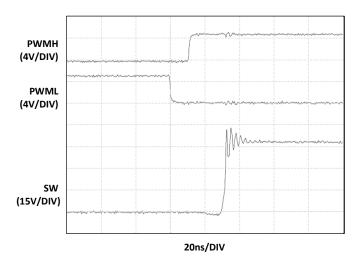

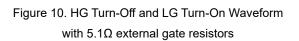

Figure 12. SW Falling Waveform at  $V_{\text{IN}}\text{=}48V$  and  $I_{\text{OUT}}\text{=}20A$

Page 8

#### **POWER THE FUTURE**

Page 9

#### **POWER THE FUTURE**

# Innoscience

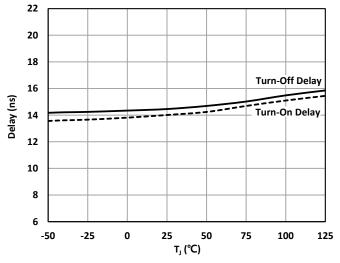

Figure 21. Low-Side Propagation Delay vs Temperature

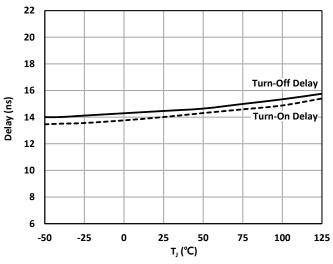

Figure 22. High-Side Propagation Delay vs Temperature

Page 10

#### **POWER THE FUTURE**

www.innoscience.com

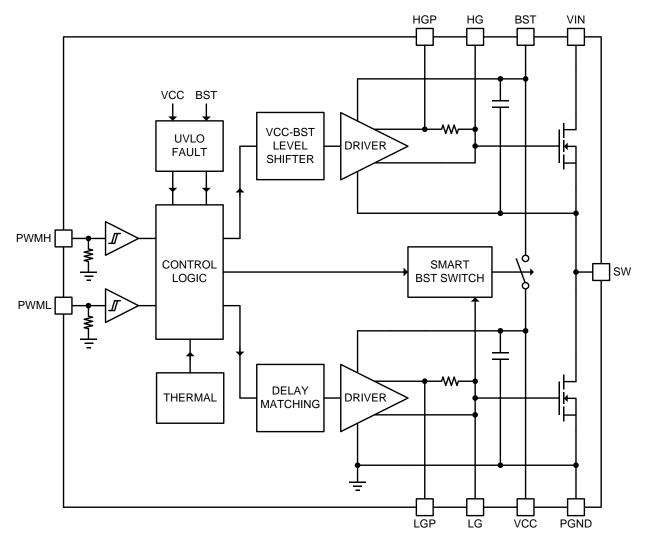

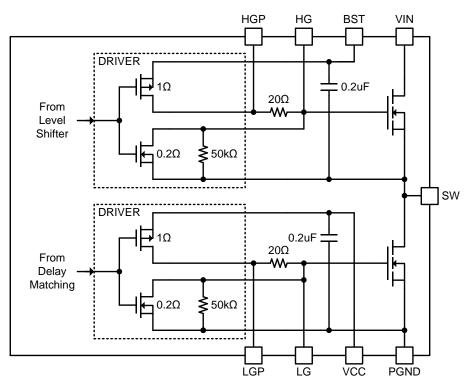

## 14. Block Diagram

Figure 23. Functional Block Diagram

Page 11

#### **POWER THE FUTURE**

www.innoscience.com

### **15. Function Description**

The ISG3202 is a 100V SolidGaN half-bridge module in a compact 5mm x 6.5mm LGA package. Within that tiny package, it integrates two high-performance enhancement-mode GaN FETs, gate drivers, gate resistors, and VCC and BST supply capacitors, offering the smallest, most efficient, and easy-to-use GaN power stage solution.

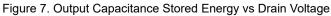

The ISG3202 features two independent and TTL logic compatible inputs to offer control flexibility. It provides split gate driver outputs for the independent control of turn-on and turn-off speeds of both high-side and low-side GaN FETs by adding external gate resistors. Active bootstrap (BST) voltage control in ISG3202 prevents overcharging of the BST supply during dead times, protecting the gate of the GaN FET. Additionally, rich fault protection is provided including independent VCC and BST undervoltage lockout (UVLO), VCC overvoltage lockout (OVLO), and over temperature protection (OTP). Highly integrated with ultra-low inductance, fast propagation delay, and superior dV/dt immunity, the ISG3202 drives next-generation high-frequency, high-power-density applications across diverse topologies including buck, boost, and buck-boost.

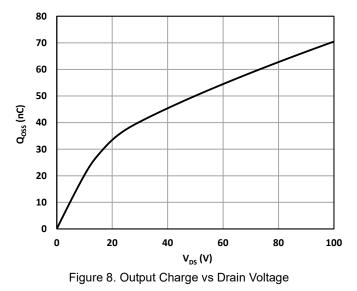

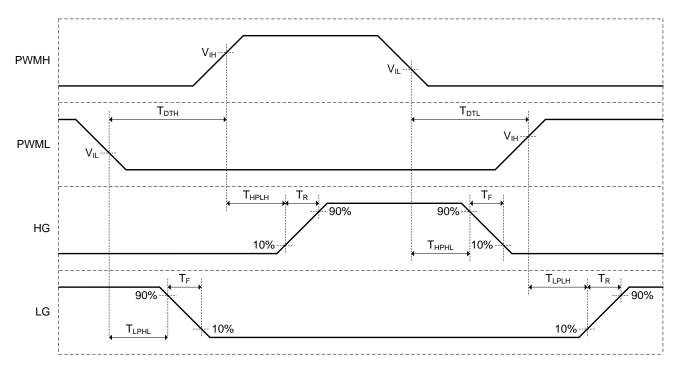

#### Input and Output

The ISG3202 input pins, PWMH and PWML, are independent and TTL logic compatible with the ability to withstand input voltages up to 5.5V regardless of VCC voltage. The ISG3202 offers fast propagation delay (14ns typical) with excellent delay matching (1ns typical) between the high-side and low-side driver channels, making it ideal for high-frequency applications. Both inputs feature a 5ns (typical) input deglitch filter to remove any unwanted pulses from a PWM input. A narrow input pulse exceeding this deglitch delay time will be extended to a minimum output pulse of 12ns (typical) to ensure proper gate turn-on and turn-off transients. Figure 24 shows the switching characteristics of the input and output. The ISG3202 allows HG and LG to overlap for turn-on; however, a carefully managed non-overlapping dead-time, T<sub>DTH/DTL</sub>, is recommended for the input interface to avoid a possible shoot-through condition. Both input pins, PWMH and PWML, have an internal pull-down resistor of 200kΩ. Table 1 shows the truth table of input and output.

Figure 24. Timing Diagram of Input and Output

Page 12

#### **POWER THE FUTURE**

| Table 1. Input and Output Truth Table |      |    |    |                      |  |  |  |  |

|---------------------------------------|------|----|----|----------------------|--|--|--|--|

| PWMH                                  | PWML | HG | LG | Comment              |  |  |  |  |

| Н                                     | L    | Н  | L  | High-Side GaN FET On |  |  |  |  |

| L                                     | Н    | L  | Н  | Low-Side GaN FET On  |  |  |  |  |

| L                                     | L    | L  | L  | Both GaN FETs Off    |  |  |  |  |

| Н                                     | Н    | Н  | Н  | Both GaN FETs On     |  |  |  |  |

#### Half-Bridge Output Stage

The ISG3202 integrates 2.4m $\Omega$ , 100V, enhancement-mode GaN FETs with drivers in a half-bridge configuration. It offers increased flexibility by providing split gate driver outputs for both high-side and low-side GaN FETs. As depicted in Figure 25, the internal gate drive output provides a default 20 $\Omega$  internal pull-up resistor. Designers can further fine-tune turn-on strength by adding an external resistor in parallel between designated pins of HGP/HG and/or LGP/LG. While turning-off the GaN FET, the integrated strong 0.2 $\Omega$  pull-down FET offers a robust, low impedance path necessary for eliminating high dv/dt induced gate turn-on. Additionally, the ISG3202 integrates the 0.2µF BST and VCC supplies capacitors within the package, thereby significantly reducing parasitic inductance loop paths and effectively minimizing voltage spikes at the gates of the GaN FETs. HG and LG pins have internal 50k $\Omega$  pull-down resistors to SW and PGND, respectively.

Figure 25. Simplified Output-Stage Block Diagram

#### VCC UVLO/OVLO Protections

The ISG3202 features UVLO and OVLO for VCC, providing the operation under the safe conditions of devices. When the VCC voltage falls below its UVLO threshold of 3.8V (typical) or exceeds above its OVLO threshold of 6.0V (typical), the ISG3202 turns off both the high-side and low-side GaN FETs and ignores the PWMH and PWML inputs.

#### **POWER THE FUTURE**

#### High dv/dt Rate GaN FET Switching

GaN FETs can switch much faster than traditional silicon based MOSFETs, requiring gate drivers capable of delivering precise and fast switching signals to fully leverage their potential. Managing high dv/dt rates during switching is important for stable gate driver circuitry, ensuring reliable and efficient operation. The ISG3202 features an advanced level-shifting technology circuit designed to overcome these challenges associated with driving GaN FETs. Its advanced noise rejection mechanism ensures precise and accurate signal transmission between the control logic to driver outputs even in extreme high dv/dt environments up to 50V/ns.

Another challenge in driving GaN FETs is the issue of high reverse conduction voltage. When the SW node drops below 0V due to this reverse conduction, it can temporarily lower the level shifter's supply rail, causing a disruption in the level shifter's output signals. This disruption can appear as a delay mismatch between signals transmitted to each side of the driver, resulting in timing inaccuracies and potential performance degradation. The proposed level shifter in the ISG3202 is designed to prevent such conditions, ensuring that delay variation is kept to a minimum (1ns typical) even when the SW node fluctuates by up to -4V. Furthermore, the ISG3202 features an additional delay matching circuit that parallels the proposed level shifter circuit, matching its process and temperature variation characteristic. This additional feature further improves delay matching to 1ns (typical).

#### **High-Side Gate-Driver Supply**

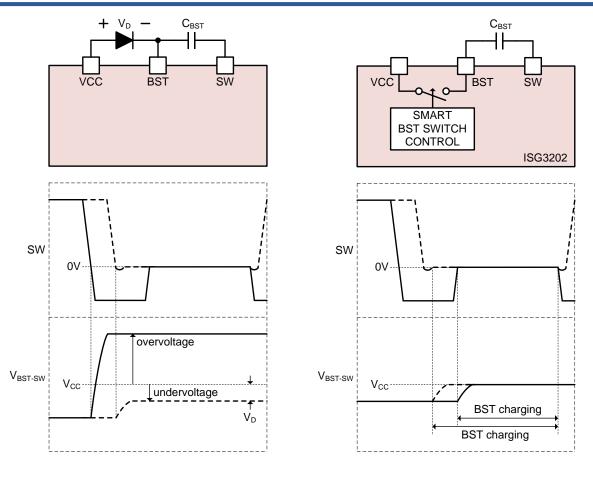

Despite GaN devices offering advantages with their superior figure of merit ( $Q_G \times R_{DSON}$ ) compared to silicon based MOSFET counterparts, their sensitivity to gate driving voltage levels presents a challenging concern. GaN devices are more vulnerable to both over-voltage and under-voltage conditions at the gate, which can have negative effects on their reliability and performance. The concern over gate over-voltage is more significant for GaN FETs, given that they are considerably more fragile compared to their silicon counterparts. Conversely, Insufficient gate voltage, or gate under-voltage, can result in increased switching losses and reduced efficiency.

To mitigate these challenges, the ISG3202 features a smart BST switch that allows precise control for BST charging and blocking. Figure 26 illustrates the operation principle of the smart BST switch. Unlike silicon MOSFETs, GaN FETs typically lack an intrinsic body diode, resulting in higher reverse conduction voltages, (typically 2V to 3V or even higher at high current) during dead time. This can lead to overcharging of the BST capacitor, potentially causing permanent damage to the gate of the high-side GaN FET. In the ISG3202, the BST switch's turning on and off are precisely controlled so that it allows charging of the BST capacitor only during SW node is fully reached at PGND voltage when the low-side power switch is being turned on. Moreover, the BST switch exhibits a low on-impedance of  $4\Omega$  (typical), ensuring minimal dropout voltage. Accordingly, the ISG3202 always maintains a well-balanced BST rail voltage close to VCC, achieving excellent delay matching and balanced gate driving strength between the high-side and low-side drivers.

Additionally, the ISG3202 provides a BST UVLO protection with a falling threshold of 3.1V (typical) and a rising threshold of 3.6V (typical). When BST-SW falls below BST UVLO threshold, the ISG3202 enters BST UVLO mode, turns off the high-side GaN FET, but the low-side driver and GaN FET remain activated.

Page 14

### POWER THE FUTURE

www.innoscience.com

# **Innoscience**

#### **Over Temperature Protection (OTP)**

The ISG3202 employs OTP. If the internal junction temperature, T<sub>j</sub>, exceeds 165°C (typical), The PWMH and PWML inputs are ignored, and both the high-side and low-side GaN FETs are turned off. When the temperature drops below 145°C (typical), the ISG3202 will resume normal operation.

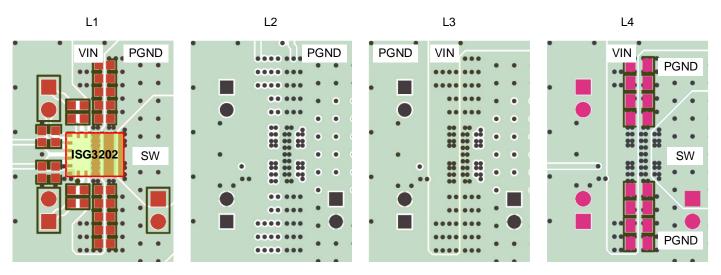

#### Layout Recommendation

Due to the small input capacitance of the GaN FET, the ISG3202 can support a high-frequency operation but it causes high dv/dt and high di/dt in power loop. To avoid the voltage and current spike caused by high dv/dt and high di/dt, the parasitic of the gate driving loop and power loop must be reduced by proper layout technique.

The ISG3202 employs an excellent layout on internal substrate to reduce the gate driving loop and power loop: (1) The driver has been placed very close to the GaN FETs to minimize the loops of parasitic inductance and reduce the noise on the gate loop. (2) The bootstrap capacitor is integrated in the module and the distance between BST and VCC to the driver has been minimized to minimize power loop impedance. (3) The distance between high-side GaN FET and low-side GaN FET has been minimized to avoid excessive voltage spike to the driver caused by the parasitic inductance between high-side GaN FET and low-side GaN FET.

Although the optimized pinout of the ISG3202 simplifies the power stage layout significantly, a proper layout of PCB board is required to fully utilize the benefit of the ISG3202. The layout guidelines are as follows:

Page 15

#### **POWER THE FUTURE**

1. The optional resistor between HGP(LGP) pin and HG(LG) pin to adjust the turn-on speed of the GaN FETs should be placed close to ISG3202.

2. The optional VCC decoupling capacitor should be placed close to ISG3202.

3. Use planes for VIN and PGND to minimize power losses and ensure effective voltage filtering. The power input decoupling capacitors should be placed close to ISG3202.

A 4-layer PCB layout example is shown in Figure 27. A two-layer board design is also possible due to the optimized pinout.

Figure 27. Four-Layer Layout Example

Page 16

#### **POWER THE FUTURE**

www.innoscience.com

### **Typical Applications**

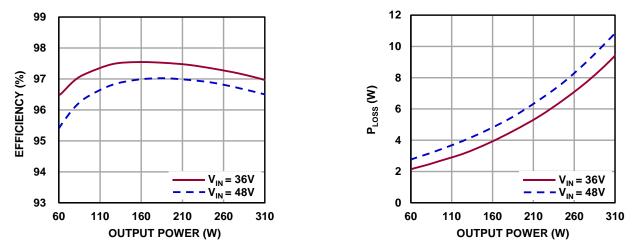

Figure 28. 36V - 80V Input, 12V Output, and 300W Buck Converter

Figure 29. Efficiency vs Output Power and Power loss vs Output Power at V<sub>OUT</sub>=12V: Refer to INNEHB100B1 Demo Board

#### **POWER THE FUTURE**

**Innoscience**

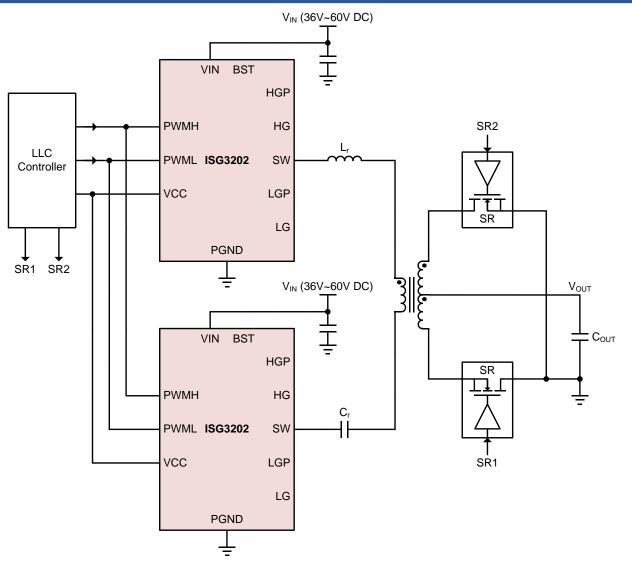

Figure 30. 36V - 60V Input, 9V - 15V Output, 1kW 4:1 non-regulated LLC Resonant Converter

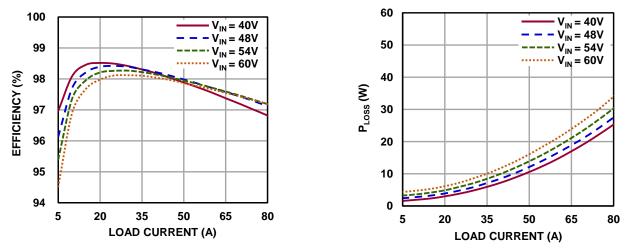

Figure 31. Efficiency vs Load Current and Power Loss vs Load Current under the Conditions of 4:1 Conversion Ratio and f<sub>sw</sub>=1MHz: Refer to INNDDD1K0A1 Demo Board

### **POWER THE FUTURE**

**I**Innoscience

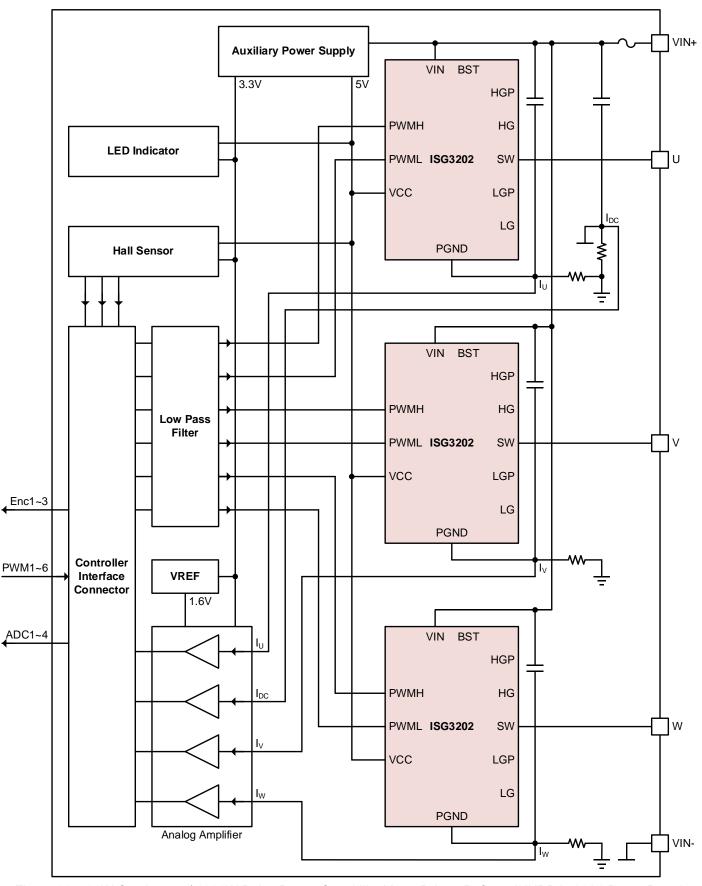

Figure 32. 500W Continuous / 1000W Pulse Power Capability Motor Driver: Refer to INNDDA500A1 Demo Board

Page 19

#### **POWER THE FUTURE**

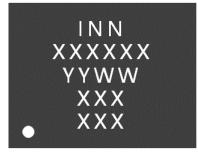

### **16. Package Information**

#### LGA5X6.5 Package:

#### TOP VIEW

SIDE VIEW

#### BOT VIEW

NOTE:

1) ALL DIMENSION ARE IN MILLIMETERS.

2) BOTTOM VIEW IS FT TESTER SIDE VIEW.

3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

4) COMPLIES WITH JEDEC MO-303.

5) DRAWING IS NOT TO SCALE.

| ROW   | Description  | Example |  |  |  |

|-------|--------------|---------|--|--|--|

| Row 1 | Company Name | INN     |  |  |  |

| Row 2 | Product Code | XXXXXX  |  |  |  |

| Row 3 | Date Code    | YYWW    |  |  |  |

| Row 4 |              | XXX     |  |  |  |

| Row 5 | Lot Code     | xxx     |  |  |  |

Page 20

#### **POWER THE FUTURE**

www.innoscience.com

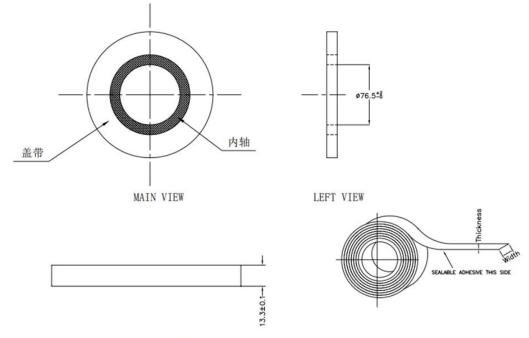

### 17. Tape and Reel Information

TECHNOLOGY SPECIFICATION[技术要求]

- 1. COVER TAPE COLOR: TRANSPARENT. [盖带颜色: 透明]

- 2. COVER TAPE THICKNESS: 48±5um. [盖带厚度: 48±5微米]

- 3. THE MATERIAL: PS[材质: 聚乙烯]

- 4. SURFACE RESISTANCE: 1×10<sup>5</sup>~1×10<sup>11</sup>Ω. [表面电阻: 1×10<sup>5</sup>~1×10<sup>11</sup>Ω]

- 5. BAN TO USE THE LEVEL 1 ENVIRONMENT-RELATED SUBSTANCES OF JCET PRESCRIBING. [禁止使用长电科技规定的一级环境管理物质]

#### **POWER THE FUTURE**

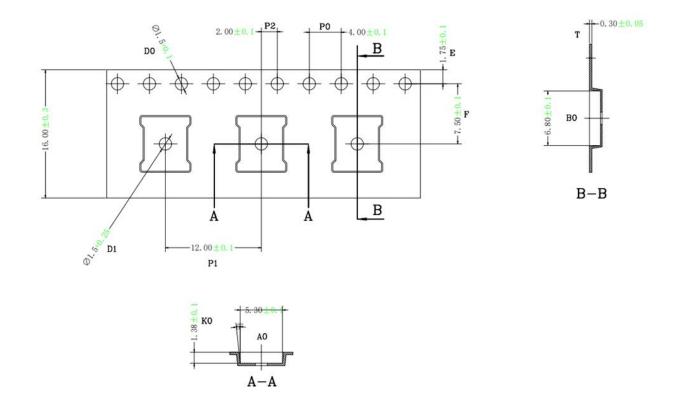

# Innoscience

TECHNOLOGY SPECIFICATION [技术要求]

1. CARRIER TAPE COLOR: BLACK. [载带颜色为黑色]

2. THE MATERIAL: PS [材质: 聚苯乙烯]

3. SURFACE RESISTANCE 1X10<sup>4</sup>~1X10<sup>9</sup>OHMS. [表面电阻为1X10<sup>4</sup>~1X10<sup>9</sup>Ω]

4. MOLD# LGA (5×6.5). [载带规格LGA (5×6.5)]

5. COVER TAPE WIDTH: 13.3±0.1mm. [配套13.3±0.1mm宽盖带]

6. TOLERANCE: X. X ±0.20 X. XX±0.10 [未注明公差参考: X. X±0.2 X. XX±0.10]

7. COVER TAPE COLOR: TRANSPARENT [盖带颜色无色透明]

8. BAN TO USE THE LEVEL 1 ENVIRONMENT-RELATED SUBSTANCES OF JCET PRESCRIBING.

[禁止使用长电科技规定的一级环境管理物质]

Page 22

#### **POWER THE FUTURE**

www.innoscience.com

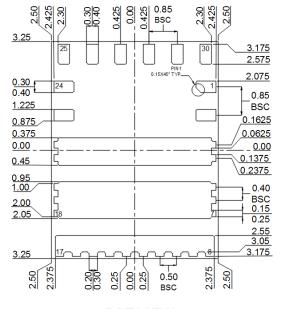

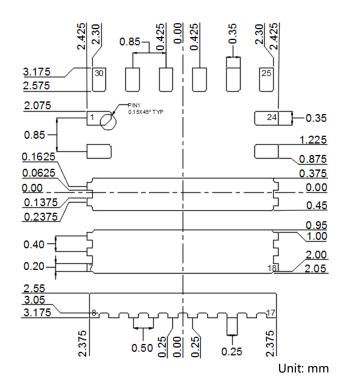

### **18. Recommended Land Pattern**

#### LGA5X6.5-30L Package:

### **19. Order Information**

| Ordering Code | Package      | Product<br>Code | MSL  | Packing<br>(Tape & Reel) |

|---------------|--------------|-----------------|------|--------------------------|

| ISG3202LA     | LGA5x6.5-30L | 3202LA          | MSL3 | 13" 2500PCS/reel         |

Page 23

#### **POWER THE FUTURE**

www.innoscience.com

### **Important Notice**

The information provided in this document is intended as a guide only and shall not in any event be regarded as a guarantee of conditions, characteristics, or performance. Innoscience does not assume any liability arising out of the application or use of any product described herein, including but not limited to any personal injury, death, or property or environmental damage. No licenses, patent rights, or any other intellectual property rights is granted or conveyed. Innoscience reserves the right to modify without notice. All rights reserved.

Page 24

#### **POWER THE FUTURE**

www.innoscience.com